ISBN: 978-81-951121-8-0

# **ICTASEMP-2021**

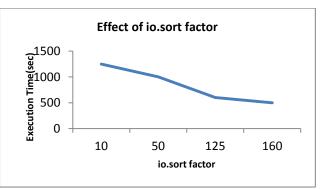

15<sup>th</sup> - 16<sup>th</sup> July 2021 Virtual Conference

# International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics

# Organized By

Department of Electronics and Communication Engineering, Holy Mary Institute of Technology & Science in Association with Institute For Engineering Research and Publication (IFERP)

# ICTASEMP-2021

# 15<sup>th</sup> - 16<sup>th</sup> July, 2021

Virtual Conference

Organized by Department of Electronics and Communication Engineering, Holy Mary Institute of Technology & Science, Telangana

*In Association with* Institute For Engineering Research and Publication (IFERP)

#### Publisher: IFERP Explore

© Copyright 2021, IFERP-International Conference

No part of this book can be reproduced in any form or by any means without prior written Permission of the publisher.

This edition can be exported from India only by publisher IFERP-Explore

## **Preface**

The "International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics (ICTASEMP-2021) - Virtual Conference" is being organized by Department of Electronics and Communication Engineering, Holy Mary Institute of Technology & Science, Telengana in Association with IFERP-Institute For Engineering Research and Publications on the 15<sup>th</sup>-16<sup>th</sup> July, 2021.

Holy Mary Institute of Technology & Science (HITS) has a sprawling student –friendly campus with modern infrastructure and facilities which complements the sanctity and serenity of the major city of Telangana.

The "International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics" was a notable event which brings Academia, Researchers, Engineers, Industry experts and Students together.

The purpose of this conference is to discuss applications and development in area of "Technological Advancement in Science, Engineering, Management & Pharmaceutics" which were given International values by Institute for Engineering Research and Publication (IFERP).

The International Conference attracted over 150 submissions. Through rigorous peer reviews 83 high quality papers were recommended by the Committee. The Conference aptly focuses on the tools and techniques for the developments on current technology.

We are indebted to the efforts of all the reviewers who undoubtedly have raised the quality of the proceedings. We are earnestly thankful to all the authors who have contributed their research works to the conference. We thank our Management for their wholehearted support and encouragement. We thank our Principal for his continuous guidance. We are also thankful for the cooperative advice from our advisory Chairs and Co-Chairs. We thank all the members of our local organizing Committee, National and International Advisory Committees.

# Acknowledgement

**Er. R. B. Satpathy** Chief Executive Officer Institute for Engineering Research and Publication (IFERP)

On behalf of Institute For Engineering Research and Publications (IFERP) and in association with Department of Electronics and Communication Engineering, Holy Mary Institute of Technology & Science (HITS), Telengana. I am delighted to welcome all the delegates and participants around the globe to Holy Mary Institute of Technology & Science for the "International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics (ICTASEMP -2021) - Virtual Conference" Which will take place from 15<sup>th</sup>-16<sup>th</sup> July, 2021.

It will be a great pleasure to join with Engineers, Research Scholars, academicians and students all around the globe. You are invited to be stimulated and enriched by the latest in engineering research and development while delving into presentations surrounding transformative advances provided by a variety of disciplines.

I congratulate the reviewing committee, coordinator (IFERP & HITS) and all the people involved for their efforts in organizing the event and successfully conducting the International Conference and wish all the delegates and participants.

Regards **Er. R. B. Satpathy**

# Message from Honorable Founder Chairman

# Dr. Arimanda Vara Prasad Reddy

Founder Chairman, HMGI Telangana, India

#### Message

I am pleased to welcome you to the International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics-2021 (ICTASEMP'21) to be held on 15<sup>th</sup>-16<sup>th</sup> July, 2021. Due to current pandemic situation, the conference will be organized in virtual mode only. This conference is from Holy Mary Institute of Technology & Science (Autonomous), Hyderabad in association with IFERP, Chennai.

The intent of this conference is not only to discuss lively and emerging issues of a particular domain but also dissemination of the awareness among other learned people. Over the years, dramatic improvements have been made in the field of Engineering, Pharmacy and Management Sciences. I hope ICTASEMP-2021 will become surely the most important International conference dedicated to bring out the Advancement in Science, Engineering, Management & Pharmaceutics.

In order to provide an outstanding technical level for the presentations at the conference, we have invited distinguished experts to participate in the Technical Programmes. We will have technical sessions, plenary sessions by keynote speakers during 2 days of conference including the awards presentation during the valedictory session on the last day of the conference.

I hope ICTASEMP-2021 will make you aware of state-of-the art systems and provide a platform to discuss various emerging technologies in Science, Engineering, Management & Pharmaceutics.

# Message from Honorable Founder Secretary

# Dr. Arimanda Vijaya Sarada Reddy

Founder Secretary, HMGI Telangana, India

#### **Message**

It is a great pleasure and an honor to extend to you a warm invitation to attend the the International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics-2021 (ICTASEMP'21) to be held on 15<sup>th</sup>-16<sup>th</sup> July, 2021. at Holy Mary Institute of Technology & Science (Autonomous), Hyderabad in association with Institute For Engineering Research and Publication (IFERP), Chennai.

The ICTASEMP'21 Conference will provide a wonderful forum for you to refresh your knowledge base and explore the Advancement in Science, Engineering, Management & Pharmaceutics. The Conference will strive to offer plenty of networking opportunities, providing you with the opportunity to meet and interact with the scientists and researchers.

I feel this ICTASEMP'21 conference is important to reiterate the need to translate Engineering & Technology into knowledge to help overcome societal challenges.

I am looking forward to meet you during the virtual conference ICTASEMP-2021 and to share a most pleasant, interesting and fruitful conference.

# Message from Chairman

### Sri. Arimanda Siddhartha Reddy

Chairman, HMGI Telangana, India

#### Message

The International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics - 2021 (ICTASEMP'21) to be held on 15<sup>th</sup>-16<sup>th</sup>July, 2021 at Holy Mary Institute of Technology & Science (Autonomous), aims to respond to the needs and aspirations of a rising global environmental issues with a theme of Advancement in Science, Engineering, Management & Pharmaceutics. ICTASEMP'21 provides an opportunity for the meeting of International Researchers, Engineers, Scientists, and specialists in the various research and development fields of Engineering and Technology.

This conference offers a premise for global experts to gather and interact intensively on the topics of Electronics and Communication, Computer Science and Information Technology along with all other Engineering streams and Pharmacy. I am privileged to say that this conference will definitely offer suitable solutions to the global issues.

I would like to express my appreciation to the organizing committee for their dedicated efforts to materialize the conference. I hope all the participants will have a fruitful and beneficial experience. Eventually I express my special thanks and appreciation to all.

## **Message from Director**

## Dr. P. Bhaskara Reddy

Director, HMGI Telangana, India

#### Message

It is my great delight to welcome you to the International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics - 2021 (ICTASEMP'21) to be held on 15<sup>th</sup>-16<sup>th</sup>July, 2021 at Holy Mary Institute of Technology & Science (Autonomous), Hyderabad in association with Institute For Engineering Research and Publication (IFERP), Chennai.The idea to host the ICTASEMP'21 in HITS, Hyderabad is to bring together Researchers, Scientists, Engineers, Scholars and Students in the areas of Information Technology, Computer Science, Electronics and Communication Engineering and all other Engineering streams and Pharmacy including Management Sciences

The ICTASEMP'21 Conference will foster discussions and hopes to inspire participants from a wide array of themes to initiate Research and Development and collaborations within and across disciplines for the advancement of Technology.

The various thematic sessions will showcase important technological advances and highlight their significance and challenges in a world of fast changes. I welcome all of you to attend the plenary sessions and oral presentations and invite you to interact with the conference participants.

## **Message from Convener**

#### Mr. Y. David Solomon Raju

Convener, ICTASEMP'21, HMGI Telangana, India

#### **Message**

It is a great pleasure and an honor to extend to you a warm invitation to attend the International Conference on Technological Advancement in Science, Engineering, Management & Pharmaceutics-2021 (ICTASEMP'21) to be held on 15<sup>th</sup>- 16<sup>th</sup> July, 2021 at Holy Mary Institute of Technology & Science (Autonomous), Hyderabad in association with Institute For Engineering Research and Publication (IFERP), Chennai

The theme of the conference is Advancement in Science, Engineering, Management & Pharmaceutics will underpin the need for participation in forums for collaborative Research and cooperation of individuals from a wide range of professional backgrounds.

The Advancement in Science, Engineering, Management & Pharmaceutics in the Conference will provide a wonderful forum for you to refresh your knowledge base and explore the innovations in Engineering and Technology. The Conference will strive to offer plenty of networking opportunities, providing you with the opportunity to meet and interact with the scientists and researchers, friends as well as sponsors and exhibitors.

I hope you will join us for a symphony of outstanding Conference, I am looking forward to meet you during the virtual conference ICTASEMP'21 and to share a most pleasant, interesting and fruitful conference.

# **Keynote Speaker**

#### Prof. (Dr.) Dipankar Pal

Professor of Microelectronics, BITS-Pilani Goa Ex-Director of North Eastern Regional Institute of Science & Technology (NERIST) – a Central University)

## Prof. Shailendra N Kulkarni

Education & Business Consultant, Dubai CEO, The Seer Oceana group, Dubai Advisor, Honourable Minister of Higher Education, Government of Nagaland, India CEO, Professor Kulkarni's Solutions Ltd. India Vice President, International Accreditation Organization (IAO), Houston, Tx, USA Former Vice Chancellor of three Universities in India

#### **Prof. Moshe Vardi** Professor at Rice University Bellaire, Texas, United States

# **ICTASEMP-2021**

15<sup>th</sup>-16<sup>th</sup> July, 2021 - Virtual Conference

# **ORGANIZING COMMITTEE**

#### **CHIEF PATRON**

**Prof. Dr. Arimanda Vara Prasad Reddy,** Founder Chairman, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Dr. Arimanda Vijaya Sarada Reddy,** Founder Secretary, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Sri. Arimanda Siddhartha Reddy,** Chairman, Holy Mary Institute of Technology & Science, Hyderabad, India

#### **PATRON**

**Prof. Dr. P. Bhaskara Reddy,** Director, Holy Mary Institute of Technology & Science, Hyderabad, India

#### **STEERING COMMITTEE CHAIR**

**Prof. Dr. B Karunaiah,** Assoc. Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

#### **CONVENER**

**Prof. Mr. Y. David Solomon Raju,** HOD-ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

#### **Co- CONVENERS**

**Prof. Mrs. K. Shyamala**, Associate Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

#### **ORGANIZING COMMITTEE**

**Prof. Dr. E Krishna Hari,** Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Dr. T. Pratibha Devi,** Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

Pr**of. Mrs. Y B T Sundari,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mrs. T. Kavitha**, Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mr. M S V R Reddy,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mr. P Ramesh,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mrs. M H Sushma Mercilin,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Ms. A. Gowthami,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mr. M. Sunder Rao,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Ms. K Manasa,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mr. R Mallikharjun,** Associate Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mr. L. Jagadeesh Naik,** Associate Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mr. M. Janardhan,** Assistant Professor – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

**Prof. Mrs. B V Jyothi Kumari,** Academic Assistant – ECE, Holy Mary Institute of Technology & Science, Hyderabad, India

# NATIONAL ADVISORY COMMITTEE

**Dr. Farooq Sunar Mahammad,** Professor & Head, CSE, Santhiram Engineering Collage, Andhra Pradesh, India

**Dr. C.Sivakandhan,** Professor, Mechanical Engineering, Nadar saraswathi college of engineering and technology, Tamil Nadu, India

Dr. Dola Sanjay. S, Principal, Ramachandra College of Engineering, Andhra Pradesh, India

**Dr. G. V. K. Murthy,** Vice Principal, Director-IQAC, PACE institute of technology & sciences, Andhra Pradesh, India

**Dr. Javeed MD,** Head Of Department, ECE, Sree Dattha Institute of Engineering and Science, Telangana, India

**Dr. M V Bramhananda Reddy,** Principal, Jogaiah Institute Of Technology And Science, Andhra Pradesh, India

**Dr. Nagamalleswara Rao Gujjar,** Professor & Principal, Mechanical Engineering, ESWAR COLLEGE OF ENGINEERING, Andhra Pradesh, India

**Dr. Shaik Altaf Hussain Basha,** Professor, CSE, Krishna Chaitanya Institute of Technology and Sciences (KITS), Markapur, India

**Dr. Sri Kalyana Rama J,** Professor, Civil, Vignana Bharathi Institute of Technology (Autonomous), Hyderabad, India

Dr.S.Saravanan, Professor, EEE, B V Raju Institute of Technology, Telangana, India

Dr.Sudha Arvind, Professor, ECE, CMR Technical Campus, Hyderabad, India

Dr. Algubelly Yashwanth Reddy, Vice Principal, Sree Dattha Group of Institutions, Telangana, India

**Dr. Ande Murali Varaprasad,** Professor, Director CIGS, St. Ann's College of Engineering & Technology, Andhra Pradesh, India

**Dr. G. Maruthi Prasad Yadav,** Professor & Head, Mechanical Engineering, Chadalawada Ramanamma Engineering College, Telangana, India

**Dr. Khasim Syed,** Vice Principal & Head, CSE, Eswar College Of Engineering, Andhra Pradesh, India

**Dr. M. Sandeep Reddy,** Head Of Department, Electrical & Electronics Engineering, Sree Dattha Institute of Engineering & Science, Telangana, India

**Dr. N. Kumaraswamy,** Dean & Professor, Civil Engineering, Vasireddy Venkatadri Institute of Engineering, Guntur, India

Dr. Prathusha. Perugu, Professor, CSE, Gates Institute of technology, Andhra Pradesh, India

**Dr. Praveen Kumar Mannepalli,** Professor, Computer Science And Engineering, LNCT University, Bhopal, India

**Dr. S.China Venkateswarlu,** Professor & Head, ECE, IARE-95 (Institute of Aeronautical Engineering-Autonomous), Hyderabad, India

**Dr. V.V.A.S.Lakshmi**, Professor & Head, CSE, Narasaraopeta Institute Of Technology, Andhra Pradesh, India

**Dr. Yogesh Yashwant Pundlik**, Head Of Department, EEE, Kamala Institute of Technology and Science, Telangana, India

**Dr.P.Ravi Kumar,** Head Of Department, Mechanical Engineering, CMR College of Engineering & Technology, Hyderabad, India

**Dr.Raffi Mohammed,** Professor, Mechanical Engineering, Ramachandra College Of Engineering, Andhra Pradesh, India

**Dr.V V S Ramachandram,** Professor, H & BS, Dadi Institute of Engineering and Technology, Anakapalle, India

Prof. P.Trinatha Rao, Professor, ECE, GITAM University, Hyderabad, India

**Prof. Nagendra Akula,** Professor, Mechanical Engineering, St.Peters Engineering college, Hyderabad, India

**Dr. A S N Chakravarthy,** Professor, CSE, JNTUK-University College of Engineering, Andhra Pradesh, India

Dr.Katta Subba Rao, Professor, CSE, B.V.Raju Institute of Technology, Telangana, India

Dr.T.S.Arulananth, Professor, ECE, MLR Institute of Technology, Hyderabad, India

# **INTERNATIONAL ADVISORY COMMITTEE**

**Dr. K. Naveen Kumar,** Professor, ECE, Al Musanna College of Technology University, OMAN, Asia

# **SCIENTIFIC COMMITTEE**

**Dr. D .Magdalene Delighta Angeline,** Assistant Professor, CSE, Joginpally B.R. Engineering College, Telangana, India

**Dr. Susarla Venkata Ananta Rama Sastry,** Associate Professor, Chemical Engineering, MVGR College of Engineering (A), Andhra Pradesh, India

Naregalkar Akshay Rangnath, Assistant Professor, Electronics & Instrumentation Engineering, V.N.R. Vignana Jyothi Institute of Engineering & Technology, Hyderabad, India

**A. Rama Prathap Reddy,** Assistant Professor, CSE, GATES Institute of Technology, Andhra Pradesh, India

**Dr Guntha Karthik,** Associate Professor, ECE, Stanley College of Engineering and Technology for Women, Hyderabad, India

**Dr K Gurnadha Gupta,** Assistant Professor, CSE, Sri Indu College of Engineering and Technology, Hyderabad, India

Dr. Amit Singh, Assistant Professor, Operations And IT, ICFAI Business School, Hyderabad, India

Dr. D. Chinni Krishna, Associate Professor, Physics, Govt. City College (A), Telangana, India

**Dr. Mohammed Mahmood Ali,** Associate Professor, CSE, Muffakham Jah College Of Engineering And Technology, Hyderabad, India

Dr. P.V.Siva Kumar, Associate Professor, CSE, VNR VJIET, Hyderabad, India

Dr. Padmavathi Papolu, Assistant Professor, Chemistry, VNRVJIET, Hyderabad, India

Dr. S. Kranthi Kumar, Associate Professor, CSE, GRIET, Hyderabad, India

**Dr. Vaibhav Mishra,** Assistant Professor, IT And Operations Management, ICFAI Business School, Hyderabad, India

**Dr. Vetriveeran Rajamani,** Assistant Professor, ECE, Nalla Malla Reddy Engineering College, Hyderabad, India

Dr.D.Srinivasa Rao, Associate Professor, Information Technology, VNRVJIET, Hyderabad, India

Dr.Naresh Kumar, Associate Professor, ECE, Vardhaman College of Engineering, Telangana, India

G.JayaLakshmi, Assistant Professor, Information Technology, V.R.Siddhartha Engineering College,

Andhra Pradesh, India

**Ganti Sree Lakshmi,** Associate Professor, ECE, Geethanjali College of Engineering and Technology, Telangana, India

**Gomasa Ramesh,** Researcher, Civil And Structural Engineering, Vaagdevi College Of Engineering, Telangana, India

**L B Bharath Raju**, Research Scholar (Mechanical Engg), National Institute of Technology, Andhra Pradesh, India

**M.Rupesh,** Assistant Professor, Electrical & Electronics Engineering, BVRIT Hyderabad College of Engineering for Women, Hyderabad, India

**Mr. K. RaviKanth**, Assistant Professor, CSE, Rajiv Gandhi University of Knowledge Technologies, Telangana, India

**Mr. K. Sreekanth,** Associate Professor, CSE, Nalla Narasimha Reddy Education Society's Group of Institutions, Hyderabad, India

**Mr. Thirupathi Allam,** Assistant Professor, EEE, Kamala Institute of Technology and Science (KITS), Telangana, India

**Mr. Vemuri Venkata Phani Babu,** Assistant Professor, Mechanical Engineering, MLR Institute of Technology, Hyderabad, India

**Ms. Bindu Swetha Pasuluri,** Assistant Professor, ECE, G Pulla Reddy Engineering College Autonomous, Andhra Pradesh, India

Omkar Naidu.V, Assistant Professor, ECE, S V College Of Engineering, Andhra Pradesh, India

Pradeep Kalakoti, Research Scholar, ECE, National Institute of Technology, Mizoram, India

**Prof.Chilukuri Bala Venkata Subbarayudu,** Associate Professor, Shadan Women's College of Engineering & Technology, Telangana, India

**S. Irfan Sadaq,** Assistant Professor, Mechanical Engineering, M.J. College of Engineering & Technology, Hyderabad, India

**Santosh Naik,** Assistant Professor, Mechanical Engineering, Hyderabad Institute of Technology and Management (HITAM), Hyderabad, India

Shashikanth K, Associate Professor, CSE, Vivekananda Institute of Technology and Science, Telangana, India

Sri.K.Prasad Babu, Assistant Professor, Chemical Engineering, CBIT, Hyderabad, India

Mr. K. Chandra Shekar, Associate Professor, CSE, GNITC – Autonomous, Telangana, India

**Dr. A. Kousar Nikhath,** Associate Professor, CSE, VNR Vignana Jyothi Institute of Engineering and Technology, Hyderabad, India

Dr. D. Narendhar Singh, Associate Professor, ECE, Anurag University, Hyderabad, India

**Dr. Korlapati Keerti Kumar,** Assistant Professor, ECE, Vaageswari College of Engineering, Telangana, India

Dr. M. Murali, Associate Professor, EEE, KSRM college of Engineering, Andhra Pradesh, India

**Dr. M.L.Pavan Kishore,** Assistant Professor, Mechanical Engineering, IFHE, Faculty of Science & Technology, Telangana, India

**Dr. Murali Vemula,** Associate Professor, English, Vidya Jyothi Institute of Technology, Hyderabad, India

Dr. V. Dinesh Reddy, Assistant Professor, CSE, SRM University, Andhra Pradesh, India

**Dr.G.Babu Rao,** Associate Professor, Civil Engineering, Narasaraopeta Engineering College, Andhra Pradesh, India

G.L.Anand Babu, Associate Professor, IT, Anurag Group of Institutions, Hyderabad, India

**Kattupalli Sudhakar,** Associate Professor, CSE, PSCMR College of Engineering and Technology, Andhra Pradesh, India

**Khaja Mannan,** Assistant Professor, CSE, Sumathi Reddy institute of Technology for women, Telangana, India

**Moguthala Shankar,** Assistant Professor, Electrical & Electronics Engineering, Siddhartha Institute of Engineering & Technology, Hyderabad, India

Nishit Kumar Srivastava, Assistant Professor, Operations And IT, ICFAI Business School, Telangana, India

R.V.Gandhi, Assistant Professor, CSE, Keshav Memorial Institute of Technology, Hyderabad, India

# S.NO.

## TITLES AND AUTHORS

| 1. | Synthesis and Low Temperature Ferroelectric Studies of Polycrystalline TbMnO <sub>3</sub><br>Multiferroics          |       |

|----|---------------------------------------------------------------------------------------------------------------------|-------|

|    | * A. Sandeep                                                                                                        |       |

|    | <ul> <li>P. Praveen</li> </ul>                                                                                      |       |

|    | ✤ M S Abdul Azeez                                                                                                   | 1-3   |

|    | <ul><li>S. Swathi</li></ul>                                                                                         |       |

|    | <ul> <li>M. Sreelatha</li> </ul>                                                                                    |       |

|    | <ul> <li>N. Pavan Kumar</li> </ul>                                                                                  |       |

| 2. | Autophagy: Readouts for Tracking the Progress of the Pathway                                                        |       |

|    | <ul> <li>Amit Mathur</li> </ul>                                                                                     | 4-7   |

|    | <ul> <li>Asmita Das</li> </ul>                                                                                      |       |

| 3. | Portable, Low Cost Ventilator                                                                                       |       |

|    | Prof. M. S. Pawar                                                                                                   |       |

|    | <ul> <li>Aniket Ghage</li> </ul>                                                                                    |       |

|    | Yug Samyak                                                                                                          | 8-10  |

|    | <ul> <li>Anurag Meshram</li> </ul>                                                                                  |       |

|    | <ul> <li>Ruchika Kokate</li> </ul>                                                                                  |       |

|    | <ul> <li>Chirag Patel</li> </ul>                                                                                    |       |

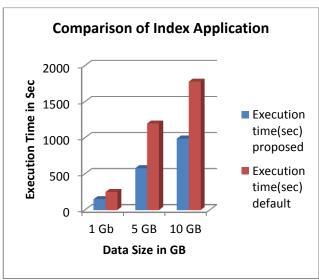

| 4. | MapReduce Parameter Optimization of Hadoop using Genetic Algorithm                                                  |       |

|    | <ul> <li>Anusha R J</li> </ul>                                                                                      | 11-19 |

|    | <ul> <li>Dr.L.RamaParvathy</li> </ul>                                                                               |       |

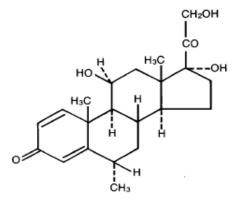

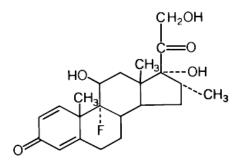

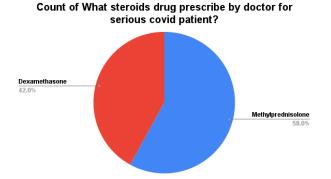

| 5. | Overuse of Steroid Drugs Methylprednisolone and Dexamethasone (Oral) Causes                                         |       |

|    | a Diabetic Patient to Become Infected With the Black Fungus in the Corona                                           |       |

|    | Virus                                                                                                               |       |

|    | <ul> <li>Ashwin Singh Chouhan</li> </ul>                                                                            | 20-25 |

|    | <ul> <li>Bharat Parihar</li> </ul>                                                                                  |       |

|    | <ul> <li>Bharti Rathod</li> <li>Ramprasad Prajapat</li> </ul>                                                       |       |

|    |                                                                                                                     |       |

| 6. | Power and Area Efficient VLSI Architecture for Fault Tolerant Method using                                          |       |

|    | Magnitude Comparator                                                                                                | 26-32 |

|    | B Chandrakanth     Mr. D Mallitharium                                                                               |       |

|    | <ul> <li>Mr. R Mallikharjun</li> </ul>                                                                              |       |

| 7. | A Novel VLSI Architecture of Truncation- And Rounding-Based Scalable                                                |       |

|    | Approximate Multiplier for High Speed Applications                                                                  | 33-36 |

|    | ✤ B Shiva Kumar                                                                                                     |       |

|    | Mr. P. Ramesh                                                                                                       |       |

| 8. | Synthesis and Elastic properties of Transition element doped La <sub>0.67</sub> Ba <sub>0.33</sub> MnO <sub>3</sub> |       |

|    | <ul> <li>B. Priyanka</li> <li>K. Krishna Taia</li> </ul>                                                            |       |

|    | <ul> <li>K. Krishna Teja</li> <li>E. Sagar</li> </ul>                                                               |       |

|    | <ul><li>E. Sagar</li><li>K. Ganesh</li></ul>                                                                        | 37-40 |

|    | <ul> <li>K. Ganesn</li> <li>M. Vishal Reddy</li> </ul>                                                              | 37-40 |

|    | <ul> <li>✓ M. Visnai Keudy</li> <li>◆ M. Sreelatha</li> </ul>                                                       |       |

|    | <ul> <li>✓ M. Stelland</li> <li>✓ T. Shekharam</li> </ul>                                                           |       |

|    | <ul> <li>N. Pavan Kumar</li> </ul>                                                                                  |       |

| L  |                                                                                                                     |       |

## S.NO.

## TITLES AND AUTHORS

| 9.  | A Cascaded Deep Network Architecture for Multi Modal Biometric Recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41-46 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

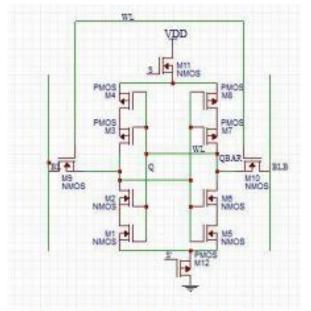

| 10. | A Novel GDI Latch for Sense Amplifier-Based Flip-Flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47-52 |

| 11. | Sun Tracking Solar Panel<br>CH. Hepsibah<br>D. Vinay Reddy<br>V. Sai Sudheera<br>T. Kavitha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53-55 |

| 12. | High Frequency Square Wave Modulation for MMC Based DC-DC SST for<br>Interconnection of HVDC Grids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56-62 |

| 13. | Design and Architecture of High Throughput Even Part CSDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63-66 |

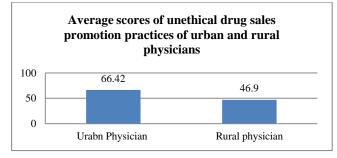

| 14. | A Comparative Analysis of Involvement of Urban and Rural Physicians in<br>Unethical Drug Promotion Practices in Madhya Pradesh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67-69 |

| 15. | Vehicles License Detection using QR Code         Image: C | 70-74 |

| 16. | Designing a Less Energy and Less-Size Shift Register for VLSI Circuit Using<br>Pulsed Handles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75-77 |

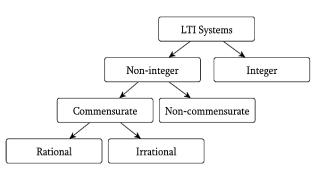

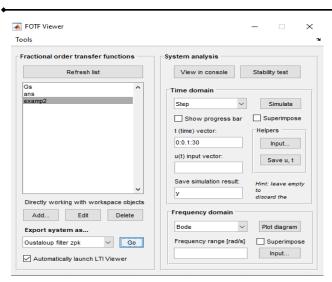

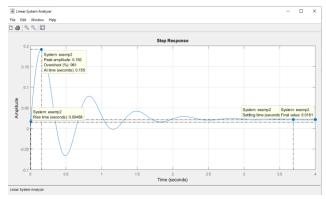

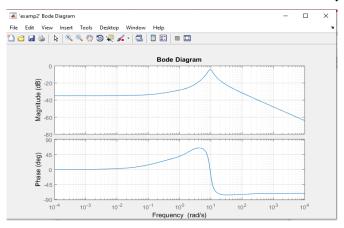

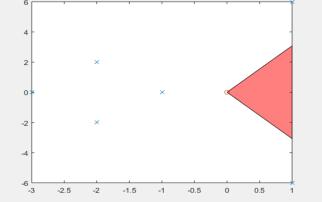

| 17. | Fractional Ordered Systems Stability through FOTF Viewer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78-83 |

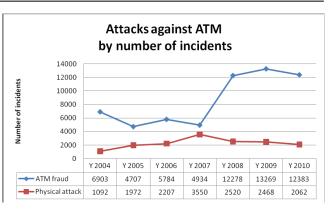

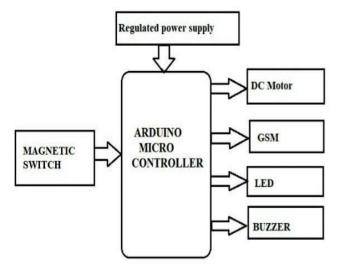

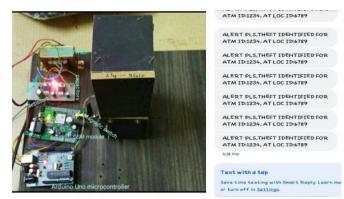

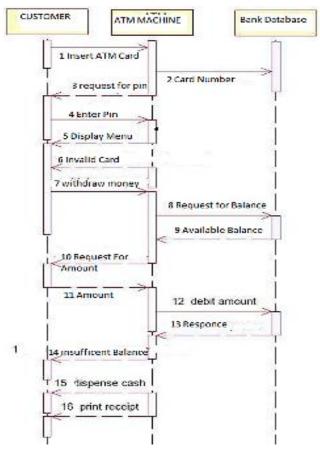

| 18. | Design and Implementation of an Advanced ATM Crime Prevention Using GSM<br>Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 84-87 |

# S.NO.

#### **TITLES AND AUTHORS**

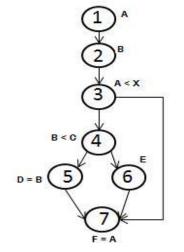

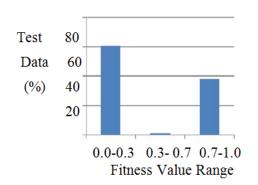

| 19. | Automatic Test Case Generation Using Genetic Algorithm                                                                                                                                                                      | 88-91   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 20. | Impact of Increase in Single Use Plastic Waste due to COVID-19 Pandemic and<br>Mitigation Measures<br>L Partha Praveen<br>P Charan Kumar<br>H Jayasree<br>D Lakshmi Shireesha                                               | 92-98   |

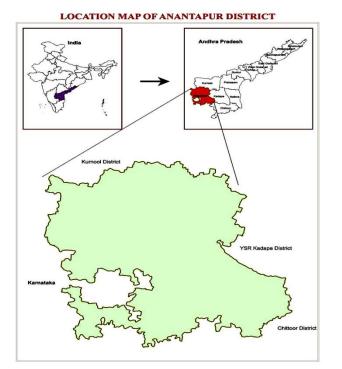

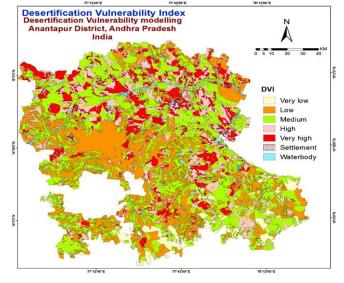

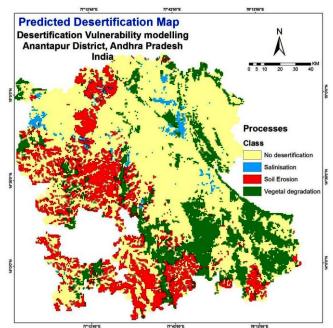

| 21. | Impact Assessment and Mitigation for Desertificatification in Anantapur District<br>of Andhra Pradesh, India                                                                                                                | 99-105  |

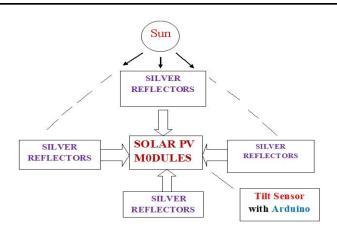

| 22. | Silver Reflective Solar Photo Voltaic System with Low Radiation Using Tilt<br>Sensor and Arduino                                                                                                                            | 106-113 |

| 23. | Synthesis and Study of Spin-Lattice Coupling in DyMnO <sub>3</sub> Multiferroics<br><b>D.Balaganesh</b><br><b>D. Rajeshwari</b><br><b>G. Ganesh</b><br><b>K. Damodar Reddy</b><br><b>Pavan Kumar</b><br><b>M. Sreelatha</b> | 114-116 |

| 24. | Smart Highway Electronic Toll Collection Using RFID Technology                                                                                                                                                              | 117-119 |

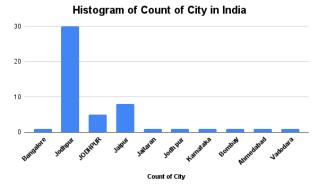

| 25. | Study the Impact of E-Commerce on Indian Economy <ul> <li>Monojit Kumar</li> </ul>                                                                                                                                          | 120-122 |

| 26. | Study of Work Life Balance of Married Working Women: A Review<br>Amrinder Kaur<br>Dr. Ramandeep Kaur Chahal                                                                                                                 | 123-130 |

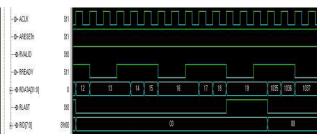

| 27. | Design and Verification of Wishbone Compliant Protocol                                                                                                                                                                      | 131-134 |

| 28. | Impact on Project Manager Role and Team Structure due to Changing Software<br>Engineering Methodologies                                                                                                                     | 135-147 |

### S.NO.

### **TITLES AND AUTHORS**

| 29. | Design and Implementation of a Prototype for Prevention of Covid-19 Spread<br>S Jyothirmaye<br>P Sai Laya<br>Kavety Kavya Shree<br>T Yuvaraj Krishna            | 148-152 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 30. | VHDL Implementation of Asynchronous GRAY Code Counter Using Reversible<br>Logic Gates      S.Deepika      T.Kavitha                                             | 153-156 |

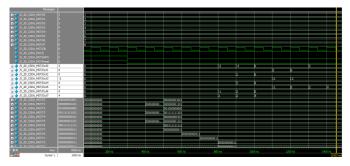

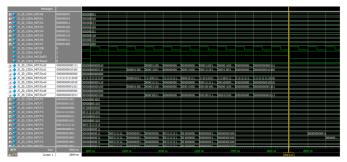

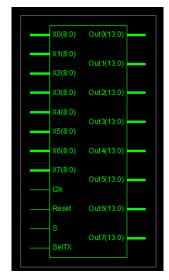

| 31. | <ul> <li>FPGA Implementation of Multibit Flip-Flop Using Mesochrnous Technique</li> <li>Samba Anusha</li> <li>Mr.M.S.Venkat Rami Reddy</li> </ul>               | 157-163 |

| 32. | Realization of Speed Optimized VLSI Architecture of Multistage Linear         Feedback Shift Register Counters Decoding Logic                                   | 164-168 |

| 33. | Quantile Regression Model for Handling Outliers in Time Series Data         *       Mr.Tushar Mehta         *       Dr.Dharmendra Patel                         | 169-173 |

| 34. | Design of Reconfigurable Architecture Using Reverse Carry Propagate Adder for<br>Energy Efficient DSP Applications                                              | 174-178 |

| 35. | Implementation of Area Optimized Hybrid LUT FPGA Architectures<br>A Shiva Kumar<br>A Gowthami                                                                   | 179-183 |

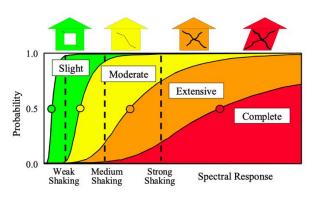

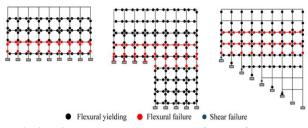

| 36. | A Review on Fragility Analysis of Bridges<br>Anshum Rana<br>Kanan Thakkar                                                                                       | 184-186 |

| 37. | A Modified Partial Product Generator for Redundant Binary Multipliers                                                                                           | 187-190 |

| 38. | Assessment of Postharvest Practices and Qualitative Status of Turmeric<br>Rhizomes from South western Ethiopia: The Case of Yeki, Sheko and Godere<br>Districts | 191-193 |

| 39. | Low Power Design Efficient Fixed Width Adder Using a Replica of Fixed Width<br>Repetition Block  Chinthakuntla Swetha  Mr.Y.David Solomon Raju                  | 194-196 |

# S.NO.

#### TITLES AND AUTHORS

| 40. | Unmanned Petrol Bunk System Using Microcontrollers                                                                               | 197-199 |

|-----|----------------------------------------------------------------------------------------------------------------------------------|---------|

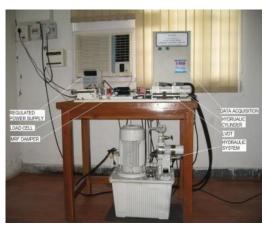

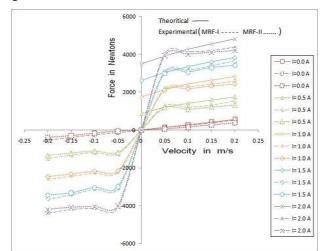

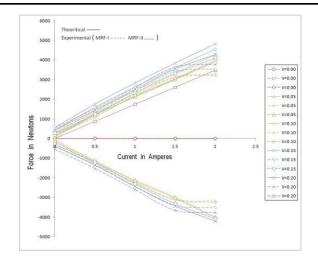

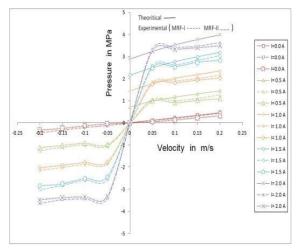

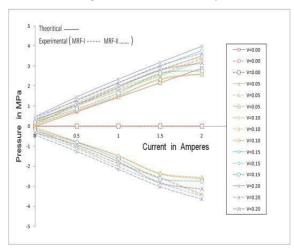

| 41. | Mathematical Modelling and Experimental Analysis of Hydro-Carbon Based<br>MRFD                                                   | 200-203 |

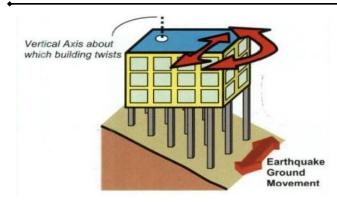

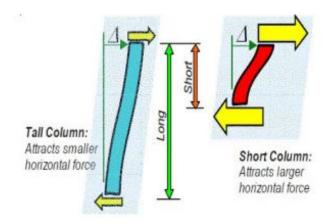

| 42. | Seismic Response of RC Building Frame Resting on Sloping Ground Using Base<br>Isolation - A Review                               | 204-206 |

| 43. | Comparison of 32-bit Vedic Multiplier with Conventional Array Multiplier                                                         | 207-209 |

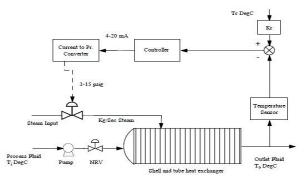

| 44. | Efficient Intelligent Controller for Heat Exchanger System                                                                       | 210-214 |

| 45. | Face Mask Detection for Preventing Respiratory Infections using Arduino UNO                                                      | 215-217 |

| 46. | Implementation Fault Tolerant Full Adder/Subtractor Using Reversible Logic<br>Gates<br>Gateboyina Prathyusha<br>Mr.M.Sunder Rao  | 218-222 |

| 47. | Area Optimized VLSI Architecture for Dynamic Accuracy Configurable<br>Multiplier using Higher Order Compressors                  | 223-226 |

| 48. | VLSI Architecture for Power Detection by using FPGA                                                                              | 227-230 |

| 49. | Area Delay Efficient Binary Adders in QCA                                                                                        | 231-234 |

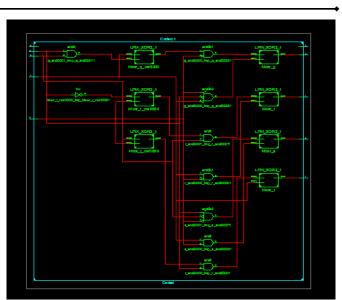

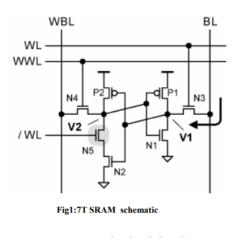

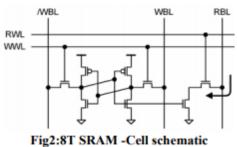

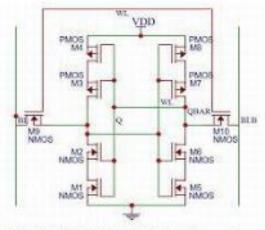

| 50. | Design and Simulation of Semicoupled 12T transistor Based SRAM USIN 15nm<br>Technology<br>Mothuku Praveen<br>Mr L Jagadeesh Naik | 235-237 |

## S.NO.

#### **TITLES AND AUTHORS**

|     | 1                                                                                                                                                                                                                    |         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

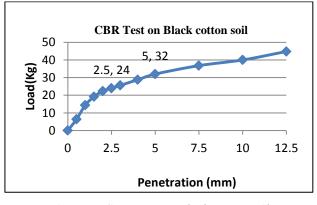

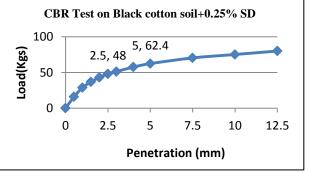

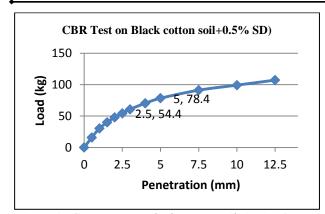

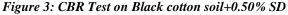

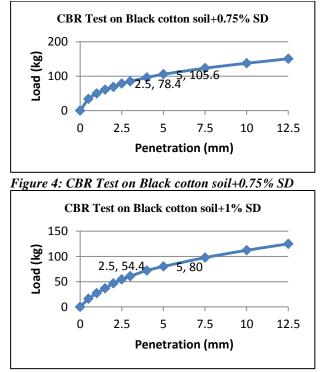

| 51. | Reinforcing the Black Cotton Soil Subgrade by Using Stone Dust <ul> <li>Mudigonda Harish Kumar</li> <li>Dr.C.Freeda Christy</li> </ul>                                                                               | 238-241 |

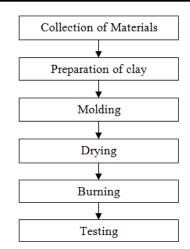

| 52. | Effectual Use of Coal Mine Waste in the Production of Eco Friendly Bricks<br>Mulla Fayaz<br>Dr. R. Venkata Krishnaiah                                                                                                |         |

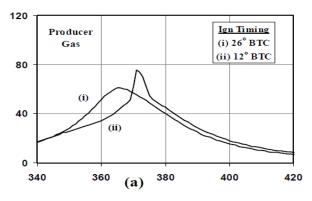

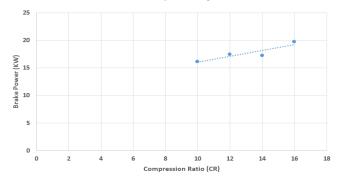

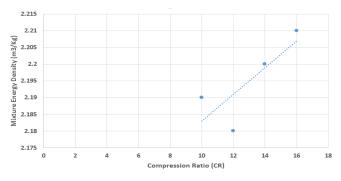

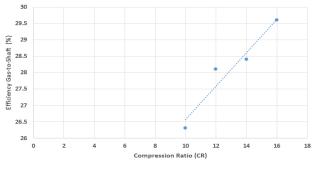

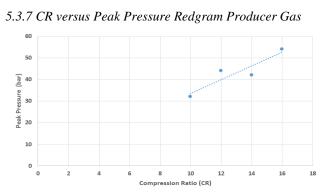

| 53. | <ul> <li>Experimental and Thermodynamic Analysis of Biomass Based Producer Gas</li> <li>Fuelled Spark Ignition Reciprocating Internal Combustion Engine</li> <li> Nerusu Pothu Raju</li> <li> Dr. M. Raju</li> </ul> |         |

| 54. | <ul> <li>Prediction on Change in Price of Bitcoins Using Machine Learning</li> <li>Ratnam Kumar Yadav</li> <li>Vishesh Thakkar</li> <li>Shubham Singh</li> <li>Ms.Aanchal Vij</li> </ul>                             | 252-255 |

| 55. | Voice-Based Email System <ul> <li>Shaik Ismail</li> <li>Chakka Lakshmi Soundarya</li> <li>Kantheti Leela</li> <li>Tallam Nagababu</li> </ul>                                                                         | 256-259 |

| 56. | Fragility Analysis of Building Structures: A Review<br>Sheenthoi Rajkumari<br>Kanan Thakkar                                                                                                                          | 260-263 |

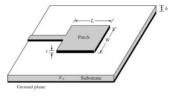

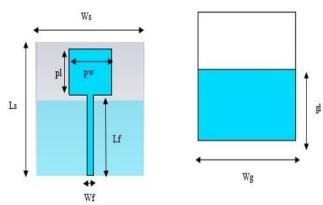

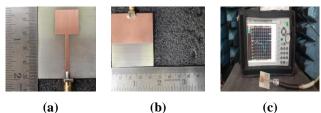

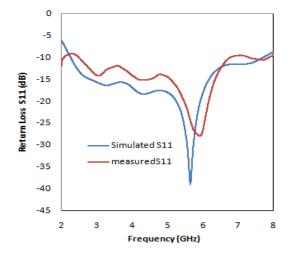

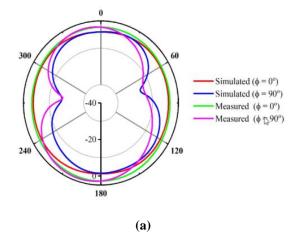

| 57. | Bandwidth Enhancement of Micro Strip Square Patch Antenna with Partial<br>Ground Plane for Wide Band Applications<br>Suneetha.Thalluru<br>Sudhakar.Alapati                                                           | 264-268 |

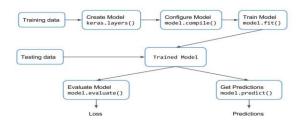

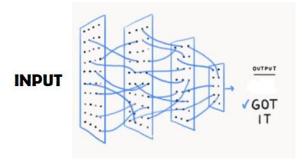

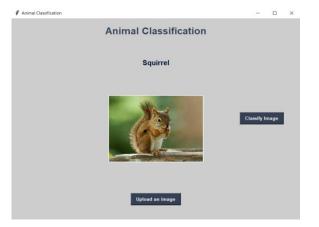

| 58. | Image Classification Using TensorFlow                                                                                                                                                                                | 269-271 |

| 59. | A Review on People Perception and Adaptability of E-Banking in India<br>Utkarsh Chirag Shandilya<br>Dr. Mohd. Farhan                                                                                                 | 272-276 |

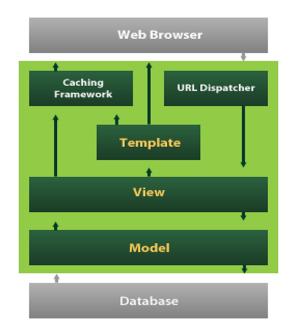

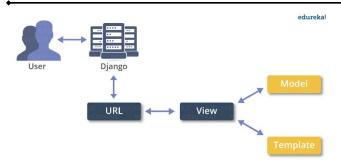

| 60. | Data Privacy in Cloud Computing, Implementation by Django, A Python-Based<br>Free and Open-Source Web Framework<br>V Veeresh<br>L. Rama Parvathy                                                                     | 277-288 |

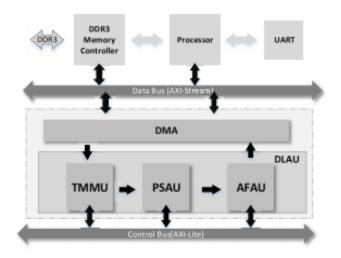

| 61. | DLAU: A Scalable Deep Learning Accelerator Unit on FPGA                                                                                                                                                              | 289-304 |

| 62. | IoT Based Advanced Dam Gate Controlling and Water Level Monitoring System<br>Using Arduino                                                                                                                           | 305-306 |

## S.NO.

#### **TITLES AND AUTHORS**

| 63. | An Advanced Embedded System for Woman Safety by Using GPS                                                                                                            | 307     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 64. | Android Controlled Robot for Detecting Metal Mines using GSM<br>G.Sravani Reddy<br>K.Mani Shanker<br>B.Rajesh                                                        | 308     |

| 65. | Comparative Analysis and Design of Solid and Multilayered Composite Pressure<br>Vessel                                                                               | 309-314 |

| 66. | Assessment on the Effects of Using Formwork Materials in Construction Sector                                                                                         | 315-318 |

| 67. | Area and Delay Optimization for Amba Bus Protocal in SOC Applications<br>Sripathi Edanna<br>Dr. E Krishna Hari                                                       | 319-323 |

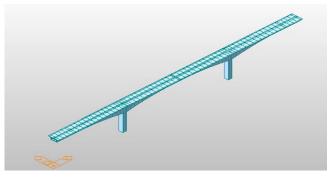

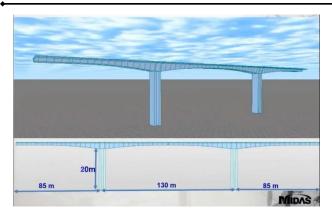

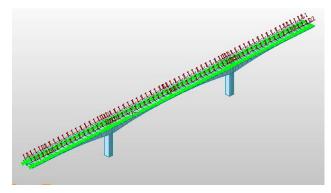

| 68. | Analysis of Precast Segmental Post-Tensioned Concrete Bridge                                                                                                         | 324-326 |

| 69. | Synthesis and Structural Studies of Eu Doped Ni-Zn Nano Ferrites<br>M S Abdul Azeez<br>D. Bala Ganesh<br>D. Rajeshwari<br>S. Swathi<br>D. Ravinder<br>N. Pavan Kumar | 327     |

| 70. | IOT Network in Indoor Environment Monitoring<br>Mrs. Ch. Sumalatha                                                                                                   | 328     |

| 71. | Gas Detection and Auto Valve Shutdown<br>CH.Shirisha<br>K. Sindhuja<br>M.Manoj                                                                                       | 329     |

| 72. | Examination Room Guide Using RFID                                                                                                                                    | 330     |

| 73. | GSM Based Home Automation Application                                                                                                                                | 331     |

## S.NO.

### **TITLES AND AUTHORS**

| 74. | Sign Language Translator                                           |     |

|-----|--------------------------------------------------------------------|-----|

|     | <ul> <li>K. Jashuva</li> </ul>                                     | 332 |

|     | <ul> <li>K. Srikanth</li> </ul>                                    | 552 |

|     | <ul> <li>M. Ravikumar</li> </ul>                                   |     |

| 75. | Design and Implementation of Automated Serving Robo                |     |

|     | Kadali Himabindu                                                   | 333 |

|     | Dasari Bindu                                                       | 555 |

|     | <ul> <li>B.Nandivardhan</li> </ul>                                 |     |

| 76. | Voice Controlled Robotic Vehicle                                   |     |

|     | M Chandana Bhavani                                                 | 334 |

|     | ✤ B Aishwarya                                                      | 554 |

|     | Ch Saipriya                                                        |     |

| 77. | Removal of Chromium from Waste Water Using Coal Fly Ash            |     |

|     | <ul> <li>V. Bhavanisree</li> </ul>                                 | 225 |

|     | P.Charan Kumar                                                     | 335 |

|     | <ul> <li>H. Jayasree</li> </ul>                                    |     |

| 78. | Mobile Charging on Insertion of Coin                               |     |

|     | * P.Apurva                                                         | 226 |

|     | T.Mounika                                                          | 336 |

|     | Y.Samhitha Reddy                                                   |     |

| 79. | Smart Helmet for Two Wheeler                                       |     |

|     | ✤ T Lokesh                                                         | 207 |

|     | ✤ R Sai Kumar Reddy                                                | 337 |

|     | S Nikhil Kumar                                                     |     |

| 80. | Knowledge Discovery from e Government Data: A Text Mining Approach |     |

| 001 | <ul> <li>Roland Vasili</li> </ul>                                  | 338 |

|     | <ul> <li>Endri Xhina</li> </ul>                                    |     |

| 81. | Solar Powered Floating Trash Collector with Water Purifier         |     |

| 01. | <ul> <li>Roniya. R</li> </ul>                                      | 339 |

|     | <ul> <li>Rajalekshmi R.S</li> </ul>                                |     |

| 82. | Implementation of Human Speed Detection Using 8051 Microcontroller |     |

| 02. | Sri Lakshmi Devika Nandyala                                        | 340 |

|     | STI Laksinin Devika Nanuyata                                       | 540 |

| 83. | GSM Based Vehicle Fuel Theft Detection System with SMS Indication  |     |

| 03. | ◆ U.Kavya                                                          |     |

|     | ↔ V.Gowtham                                                        | 341 |

|     | <ul> <li>V.Gowtham</li> <li>P Sai Nikhita</li> </ul>               |     |

|     | V I Dai IVIKIIIta                                                  |     |

# **ICTASEMP-2021**

15<sup>th</sup>-16<sup>th</sup> July, 2021 - Virtual Conference

# DADERS

Organized by Department of Electronics and Communication Engineering, Holy Mary Institute of Technology & Science, Telangana

> In Association with Institute For Engineering Research and Publication (IFERP)

15<sup>th</sup>-16<sup>th</sup> July, 2021 – Virtual Conference

# Synthesis and Low Temperature Ferroelectric Studies of Polycrystalline TbMnO<sub>3</sub> Multiferroics

<sup>[1]</sup> A. Sandeep, <sup>[2]</sup> P. Praveen, <sup>[3]</sup> M S Abdul Azeez, <sup>[4]</sup> S. Swathi, <sup>[5]</sup> M. Sreelatha, <sup>[6]</sup> N. Pavan Kumar

<sup>[1][2][3][5][6]</sup> Matrusri Engineering College, Saidabad, Hyderabad, India <sup>[1][2][3]</sup> Department of Physics, Osmania University, Hyderabad, India

<sup>[4]</sup> Department of Physics, AV College of Arts, Science and Commerce, Domalguda, Hyderabad

simultaneously more primary Abstract—Multiferroics are the materials that possess ferroic two or (electric/magnetic/elastic/toroidic) properties. The possible applications of multiferroics are ac/dc sensors, microwave resonatorphase shifters, multi-state memories, solar cells, and thermal energy harvesting, and magnetocaloric materials. Among various types of single-phase multiferroics, Giant spin-driven ferroelectric polarization has been reported in single-crystal TbMnO<sub>3</sub> multiferroics under high pressure. A polycrystalline TbMnO<sub>3</sub> was synthesized through the sol-gel method and structural studies revealed the single-phase nature of the sample. Rietveld analysis has been used to analyze the structural results and to calculate the lattice parameters. Ferroelectric studies have been studied from the 4-50K temperature range and the results revealed that the specific results are well matching with ferroelectric transitions. These studies revealed the coupling between the ferromagnetic and ferroelectric orders.

Index Terms- Multiferroics, single-phase; Heat Capacity; Dielectric Constant

#### I. INTRODUCTION

Multiferroics term was first brought into usage by H. Schmid to describe materials that show more than one primary ferroic properties like ferromagnetism, ferroelectricity, magnetoelectricity in a single-phase<sup>1</sup>. The origin of magnetism is due to the presence of localized electrons in the partially filled d or f sub-shells in rare-earth ions. Nowadays this definition is expanded to fit antiferromagnetism and ferrimagnetism. Multiferroics materials are solid-state compounds, which exhibit two ordered states are magnetic and electric. These materials are very much interested in Research & Technological application due to their coupling between Ferro phases and the piezoelectric properties facilitate a direct control of Ferromagnetic and ferroelectric properties<sup>2</sup>.

This Mechanism was used in such as actuators, switches, magnetic field sensors, and also electronic memory devices<sup>3,4</sup>. Typical multiferroic materials are transition metal oxides and also include rare earth manganite and (RMnO<sub>3</sub>) such as TbMnO<sub>3</sub>, DyMnO<sub>3</sub>, and some bismuthbased compounds like BaNiF<sub>4</sub>, BiMnO<sub>3</sub>. Here TbMnO<sub>3</sub> is a single-phase perovskite-type manganite with polycrystalline orthorhombic structure. Although there are many studies on magnetic, Heat capacity, magnetocaloric properties of TbMnO3 from room temperature to low temperature, a very few have concentrated on lowtemperature ferroelectrics properties of polycrystalline TbMnO<sub>3</sub>. In this paper, the preparation of one such compound TbMnO3 synthesized through the sol-gel method, and its ferroelectric behavior in low temperature has been studied and the results are discussed in the paper.

#### **II. EXPERIMENTAL METHODS**

#### 2.1 Synthesis & Characterization

The polycrystalline TbMnO<sub>3</sub> sample has been prepared through the Sol-Gel method. The starting materials Tb<sub>2</sub>O<sub>3</sub>(Sigma Aldrich, 99.99%), freshly prepared MnCO<sub>3</sub> precursors were taken in stoichiometric ratio. The materials are dissolved in Nitric acid separately and then mixed in a glass beaker on a magnetic stirrer until it gets to a homogenous solution. Then citric acid has been added to the solution and mixed for 30 mins in the ratio of 1: 1. Further, PH has been adjusted to 7 with the help of Ammonia solution. Later this solution was heated on a magnetic stirrer with a hot plate until it was reduced to (1/3)rd of its original solution at 80 °C until the viscosity of the solution increases up to a point where the solution is no longer in a liquid state but is in a semi-solid gel state. After that Ethylene glycol (CH<sub>2</sub>(OH).CH<sub>2</sub>(OH)) was added to the final solution in the ratio of 1: 1.2, and continue to heat the solution until the water content evaporates completely at around 120-150°C. The gel form in the glass beaker was further heated until we get a black-colored powder. For experimental purposes, the black-colored powder was transported into a mortar and grind to get a fine powder. After obtaining fine powder from it was calcinated at 1000 °C for four hours to remove any residual organic impurities. Later the black-colored ash will be pressed into pellets with a diameter of 10 mm and thickness of 1.5 mm, with the help of a hydraulic press by applying pressure of 2 to 3 tons per square inch. Finally, the pellets were sintered at the temperature of 1300 °C for 5hrs.

Synthesis and Low Temperature Ferroelectric Studies of Polycrystalline TbMnO3 Multiferroics

| Table 1: XRD Analysis |                     |       |  |

|-----------------------|---------------------|-------|--|

| S.No                  | XRD results         |       |  |

| 1                     | a(A)                | 5.8   |  |

| 2                     | b(A)                | 7.4   |  |

| 3                     | c(A)                | 5.3   |  |

| 4                     | V(A)                | 227.5 |  |

| 5                     | R <sub>p</sub>      | 8.25  |  |

| 6                     | R <sub>WP</sub>     | 11.05 |  |

| 7                     | R <sub>EXP</sub>    | 8.33  |  |

| 8                     | S (goodness of fit) | 1.32  |  |

#### III. RESULTS AND ANALYSIS

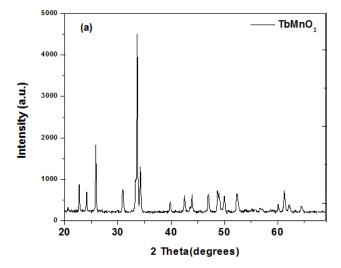

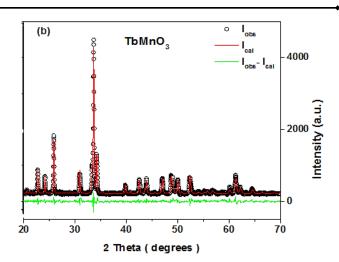

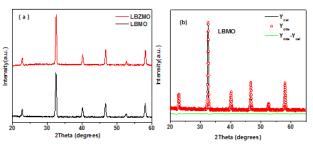

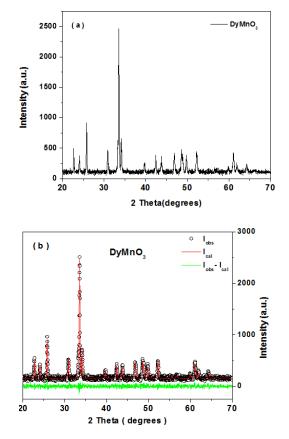

The structural characterization of samples was carried out by the XRD(X-ray diffractometry), the diffraction patterns are mentioned in Figure 1. The XRD data were analyzed using the Rietveld refinement technique by assuming orthorhombic structure with *the Pnma* space group. The data of XRD of all the samples are shown in Fig 1(a). It is clear that samples are of a single phase with no detectable impurity and the sharp peaks seen in the XRD pattern; indicate that the studied sample to be purely crystalline.

The observed and calculated Rietveld refinement patterns of TbMnO<sub>3</sub> lattice parameter values are in the given Table (1). The lattice parameters a, b and c values as 5.8Ű, 7.4 Ű, 5.3 Ű respectively, and the results have matched with the theoretical and experimental values, and also best of fit(GOF) was matched with the data in the literature. The values of residual factor  $R_p$ ,  $R_{wp}$  are satisfactory range as per literature.

Figure 1: (a) XRD of TbMnO<sub>3</sub> sample. (b) Rietveld refinement pattern of TbMnO<sub>3</sub> samples.

#### **3.1 Heat Capacity Studies**

The heat capacity of a substance of 1 gm is defined as the amount of heat required to raise its temperature by 1° C. Heat capacity can be measured at either volume constant ( $C_v$ ) or pressure( $C_p$ ). Heat capacity is important because this will give the information about the sample to how long the heating or cooling process will take at under a given heat supply.

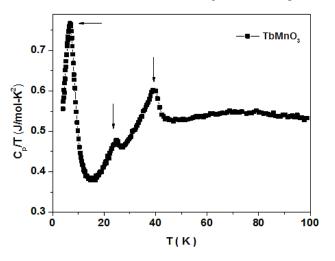

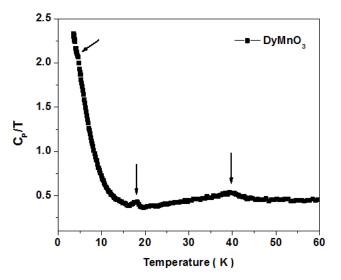

By using semi adiabatic pulse method, the Heat capacity measurements were carried out. The given figure shows the graphical variation between the ( $C_P/T$ ) with the temperature (T), to all the samples are at zero and with having magnetic fields. From the figure, the given sample exhibits approximately a sharp peak at 40 K and is attributed to the sinusoidal arrangement of  $Mn^{3+}$  ions. The other transition at about 26K is called lock-in-transition and is due to the change in the sinusoidal ordering of  $Mn^{3+}$  ions into spiral ordering which induces the breaking in the center of symmetry leads to the polarization. On further decreasing the temperature, another anomaly has been observed at below 10 K and it indicates the ordering of Tb<sup>3+</sup> ion spins<sup>5</sup>.

Figure 2: Variation of Cp/T with temperature

Synthesis and Low Temperature Ferroelectric Studies of Polycrystalline TbMnO3 Multiferroics

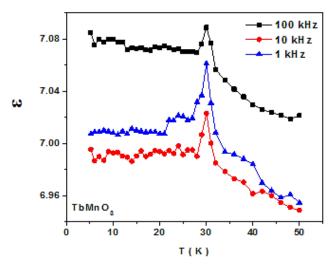

#### **3.2 Low Temperature Dielectric Constant Studies**

#### REFERENCES

- [1] Hill N A J. Phys. Chem. B 104(2000) 6694

- [2] W Prellier W, M P Singh M P and P Murugavel J. *Phys.: Condens. Matter* 17(2005) R803

- [3] Bibes M and Barthelemy A Nat. Mater7(2008) 425

- [4] Ramesh R and Spaldin N A 2007 Nat. Mater. 6 21

- [5] T. Kimura, S. Ishihara, H. Shintani, T. Arima, K.T. Takahashi, K. Ishizaka, Y. Tokura, Phys. Rev. B 68 (2003) 060403 (R).

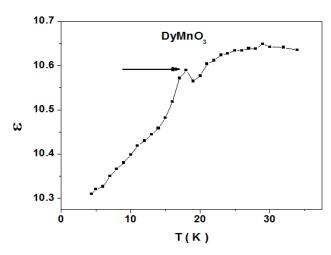

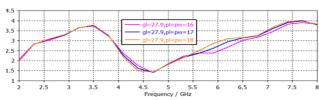

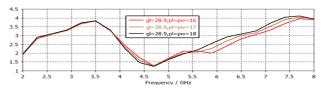

Figure-3 shows the dependence of the dielectric constant as a function of temperature at 1 kHz, 10 kHz, and 100 kHz frequencies. It has been observed that there is a slight change in dielectric constant values with the frequency. As the temperature decreases from 50K, dielectric constant values are found to increase and an anomaly has been observed at 30 K. It is matching with the anomaly in heat capacity studies. This is a paraelectric to ferroelectric transition at  $30K^5$ . It is known that ferroelectricity arises when there is a break in the center of symmetry. At this temperature, a change from the sinusoidal ordering of Mn<sup>3+</sup> ions changes to spiral ordering which breaks the symmetry. The break-in center of symmetry leads to the polarization and dielectric constant.

Figure 3: Variation of frequency with Temperature for different compounds.

#### **IV. CONCLUSIONS**

Polycrystalline TbMnO<sub>3</sub> has been prepared through the solgel method. Structural analysis has been carried out by using X-ray diffraction and observed that the samples crystallized in orthorhombic structure without any secondary phases. Heat capacity measurements revealed the multiple transitions in the material at 40K, 26K and below 10K are attributed to the ordering of  $Mn^{3+}$  and  $Tb^{3+}$  ions. Low-temperature dielectric constant studies revealed a transition at 30K which is ferroelectric transition. It is well matching with the heat capacity results.

#### V. ACKNOWLEDGEMENTS

The authors would like to extend their sincere thanks to Prof. P. Venugopal Reddy for his guidance and encouragement. The authors thank Dr. A.M. Awasthi for providing a low-temperature Dielectric permittivity facility. The authors also thank Dr. R. Rawat and Pallab Bag for heat capacity measurements.

15<sup>th</sup>-16<sup>th</sup> July, 2021 – Virtual Conference

# Autophagy: Readouts for Tracking the Progress of the Pathway

<sup>[1]</sup> Amit Mathur, <sup>[2]</sup> Asmita Das

<sup>[1][2]</sup> Department of Biotechnology, Delhi Technological University, Delhi, India

Abstract—Autophagy is a highly regulated cellular pathway aiming to maintain and establish homeostatic state of cells. Autophagy is a form of programmed cell death pathway that keep an eye on non-functional proteins/organelles, intracellular pathogens, endoplasmic reticulum and oxidative stress some external stimuli like hypoxia, nutrient deprivation, specific drug molecules etc. This process starts by formation of a double membrane structure called autophagosome which ultimately delivers the target cargo to lysosomes for degradation. Autophagy has a debatable role in cancer progression as in some studies it is seen that it supports cancer progression while in others it shows cancer regression. This pathway is very crucial in regulating overall physiological state of cells Therefore it becomes very important to keep surveillance on this pathway. Tracing this pathway can lead to prediction of large spectrum of pathological conditions and also the efficacy of therapeutics. This review focuses on some indirect and direct methods that are applicable in lab setup to track this critical cellular pathway.

Index Terms— Autophagy, Cancer, Endoplasmic reticulum, Hypoxia, Lysosomes

#### I. INTRODUCTION

Autophagy is a conserved self degradative pathway which was first discovered and explored in yeast by Yoshinori Ohsumi in 2016. He was honoured with Noble Prize in the field of Medicine or Physiology but the term "Autophagy" was given by Christian de Duve way back earlier [1]. In the last two decades prodigious work has been done in the field of exploring autophagic pathway, identifying autophagy related genes (ATGs) and understanding all the protein complexes involved in the pathway. Typically three forms of autophagy are seen in the cell namely, macroautophagy, mitophagy (mitochondrial autophagy) and chaperone mediated autophagy (targets KFERQ motif in target protein). Apart from this xenophagy (autophagy mediated pathogen killing), aggrephagy (autophagy mediated lysis of aggregated proteins) are also seen. Interestingly autophagy also plays key role in some pathological conditions like neurodegenerative disorders [2], cardiovascular diseases [3] and autoimmune disorders [4]. This pathway grossly involves formation of double walled "autophagosome" which engulfs the target cargo and followed by fusion of outer membrane of autophagosome with that of lysosome resulting into a structure called "Autophagolysosome" therefore, causing its degradation via the lytic enzymes in lysosomes. Autophagic pathway is divided into 4 sub stages:

#### **INITIATION:**

In the first stage of starvation mediated autophagy mechanistic target of rapamycin complex 1 (Mtorc1) dissociates from unc-51-like autophagy-activating kinase 1 (ULK1/2) complex and ATG13 protein leading to their activation. ULK1/2, ATG13, ATG101 and FIP200 form the initiation complex for phagophore formation [5].

#### NUCLEATION:

The next step is nucleation of the initiation complex in which class III phosphatidylinositol 3-kinase (PtdIns3K) plays a central role. The key protein complexes in the step are VPS34, UV irradiation resistance-associated gene (UVRAG), BECLIN1. Together these complexes facilitate the nucleation step [5]. Some anti-apoptotic proteins like BCL-xL, BCL-2 and other proteins like Rubicon interacts with BECLIN1and suppress its expression [6] ultimately affecting immature autophagosome formation.

#### **ELONGATION:**

Atg12–Atg5-Atg16 protein complex is requisite for elongation of immature autophagosome in both yeast and mammals. Ubiquitin systems like microtubule-associated light-chain B (LC3B) in conjugation with lipidated phosphatidylethanolamine (PE) helps in membrane tethering and closing phagophore to form mature autophagosome. Combination of lipidated LC3B and Atg12–Atg5-Atg16 complex marks elongation and closing of autophagosome [5].

#### FUSION AND FEED DEGRADATION:

In the last step the autophagosome fuses with outer membrane of lysosomes resulting into autolysosome with the help of Rab GTPase and SNARE proteins [5].

#### METHODS FOR AUTOPHAGY READOUTS:

Autophagy is a zestful pathway and is more of an adaptive response to various types of stresses. As already discussed this process plays key role in various cellular processes including ageing, control of cell density, cellular homeostasis, maintenance of stemness in cancer cells etc. Therefore it becomes extremely important and needful to keep a track and monitor this process as failure at any step could lead to various pathologies (cancer, neurodegenerative disorders, and cardiovascular diseases).

Autophagy: Readouts for Tracking the Progress of the Pathway

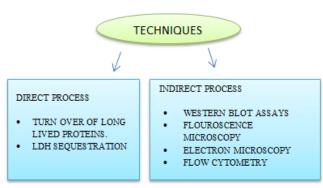

Two ways of autophagic flux detection has been briefly discussed here:

#### FIGURE 1- OUTLINE DEPICTING DIFFERENT WAYS OF ANALYSING AUTOPHAGIC FLUX.

#### **INDIRECT METHODS:**

A. WESTERN BLOT ASSAYS: One of the widely used indirect method of estimating autophagic flux, in this different autophagic substrates can be targeted and be analysed on a western blot or SDS PAGE. One approach is to use microtubule-associated protein 1 light chain 3 (MAP1-LC3) protein family, these are grouped as GABARAP and LC3 subfamilies. LC3 protein family has role to play in phagophore formation and closure as explained earlier in the text. LC3 proteins are found on outer and internal surface of autophagophore membrane. LC3 protein present on inner side of membrane gets delivered to lysosomes along with the cargo. Lipidated form of LC3 or LC3-II (Molecular weight14-16 KDa) and non lipidated LC3 or LC3-I (Molecular weight 16-18 KDa) this causes separation of protein via western blotting. Lysosomal inhibitor (like chloroquine, Bafilomycin) presence or absence in analysis of LC3-I/ LC3-II gives a hazy picture as increased LC3-II concentration may indicate dysfunctional autophagosome and lysosome fusion or dysfunctional induction of autophagy while decreased LC3-II concentration may indicate autophagy inhibition or increased autophagic flux. To check inhibition or stimulation of autophagy we can analyse LC3-II amount in existence and inexistence of lysosome blockers in same sample [7].

Second approach is estimation of SQSTM1/p62- is important autophagic substrate that helps in anchoring autophagic cargo proteins inside autophagosome by hooking onto their ubiquitin binding domain, moreover they convey the cargo to LC3-II via LC3 interacting region (LIR). Just like LC3-II estimation via western blotting SQSTM1/p62 can also be estimated in presence and absence of lysosomal blockers, increased levels of the complex indicate dysfunctional autophagic flux and decreased levels of this shows high levels of autophagic flux. A problem with this approach is some tissues and cells tend to have steady levels of SQSTM1/p62 even in presence of autophagy, because its expression is transcriptionally regulated and hence balanced by de novo synthesis. This makes abnormal western blot results but some studies afterwards showed that cycloheximide is a compound that blocks de novo pathway and further analysis can be done by radiolabelling pulse chase experiments and immuno-precipitation (of SQSTM1/p62) [7], [8].

- B. FLOUROSCENCE MICROSCOPY: This indirect method allows qualitative and quantitative estimation of autophagy marker, substrates or proteins by immunofluorescence or live cell imaging [7]. Generally endogenous autophagy proteins or ectopically expressed proteins are utilised. These proteins can even be prepared by transfection ,stably transfected cell lines gives homogenous protein expression and low signal variability, therefore it is preferred in live cell microscopy and imaging [9]. FM (FLOUROSCENCE MICROSCOPY) Method can be performed by three approaches (i) Dyes- Some amphiphilic tracer dye, like Cyto-ID® can be used for tracking autophagic process by visualising microscopically in live cells and for cells difficult for transfection. Advantage being efficient, accurate and reliable and can be performed in difficult experimental setting, disadvantage being partial specificity [10].

- C. ELECTRON MICROSCOPY: Electron microscopy directly allows autophagosomes, autophagolysosome, to be detected through eye, although it is easier said than done because it is very difficult to distinguish these ultra-cellular structures through naked eye morphologically. Adding to this tracking through h EM becomes difficult as there are some factors which govern its success like - well preserved cell morphology, cell type, use of lysosomal inhibitors, procedure for sample preparation, observational skills, cell volume [7]. An increase in autophagosome, autophagolysosome, amphisome indicate towards increased autophagic flux. Different variants of EM can be used as autophagy readouts like cryo-soft X-ray microscopy, transmission and immuno-Electron microscopy, electron tomography [11].

An increase in autophagosomal vesicle reflects increase in induction of autophagy but is not true in every sense sometimes it may indicate blockage of overall autophagic flux [12] or it may indicate dysfunctional autophagic process. Therefore direct methods seem to be more reliable.

**D. FLOW CYTOMETRY**: Method of imaging flow cytometry (combination of fluorescent microscopy and flow cytometry, unique in collecting their real and fluorescent images) and flow cytometry is helpful in cells that have poor adherence or are in suspensions. The advantage with using imaging flow cytometry is that signal location can be detected within the cell. GFP tagged LC3 (Microtubule-associated protein 1A/1B-light chain 3) could be used to monitor LC3 protein's movement into lysosomes where its degradation will cause decreased luminescence and will guide towards autophagic flux. Apart from this autophagic substrates

Autophagy: Readouts for Tracking the Progress of the Pathway

like p62,SQSTM1,NBR1 can also be tagged with green fluorescent protein and tracked for fluorescent quenching [13],[14]. One weak point of this is type of cell used, as it not very helpful in adherent cells but very effective for high content screens and monitoring of autophagy using fluorescent images [15].

#### **DIRECT METHODS:**

E. TURN OVER OF LONG LIVED PROTEINS: Long lived proteins are proteins that have high half life values and have an impact on age and other age related parameters. This method involves radiolabelling of elements like Carbon, Hydrogen, Sulphur in amino acids like leucine, leucine (radiolabel hydrogen), and methionine respectively. The radioactivity due to these labelled amino acids is measured by liquid scintillation counting during their degradation in autophagolysosome. [16]. This method is carried out in pulse-chase manner where radiolabelled compounds are added in the pulse phase and during the chase phase respective natural compound is added along with an autophagic inhibitor (Eg. 3 methyl adenine) [17]. MG132 (carbobenzoxy-Leu-leucinal) can be used to prevent proteasome degradation of these proteins.

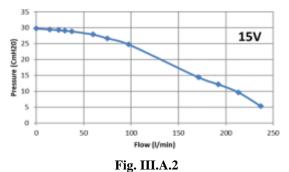

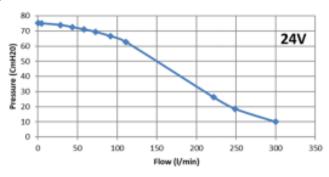

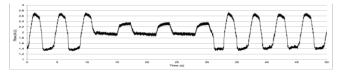

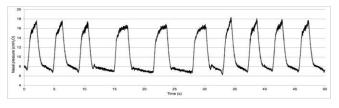

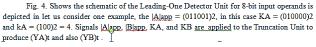

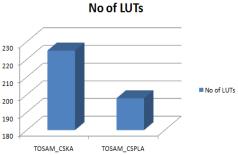

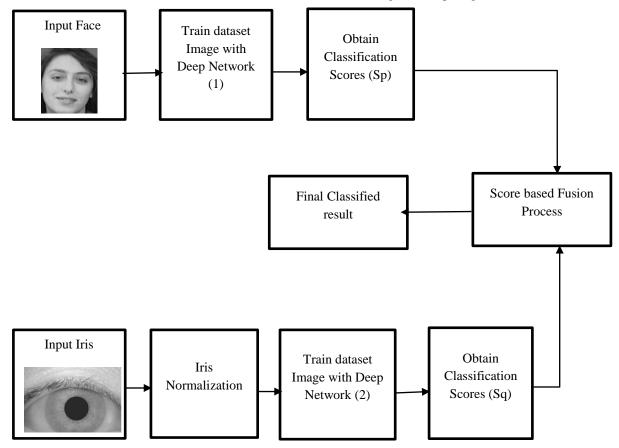

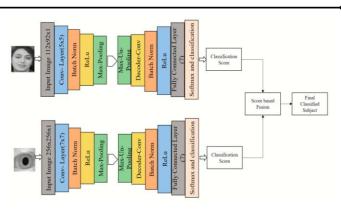

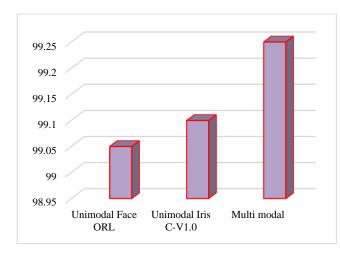

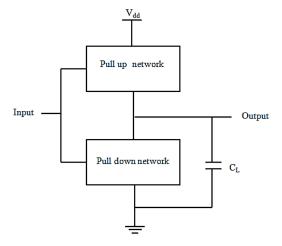

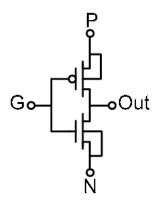

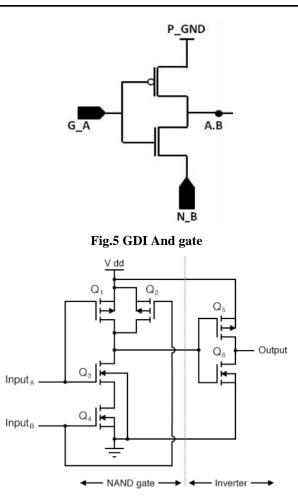

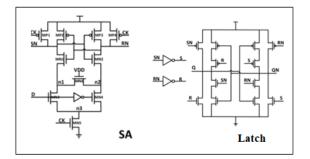

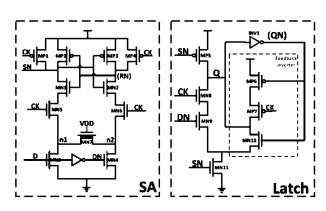

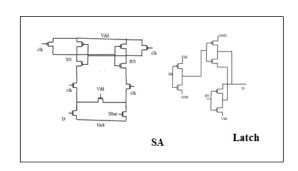

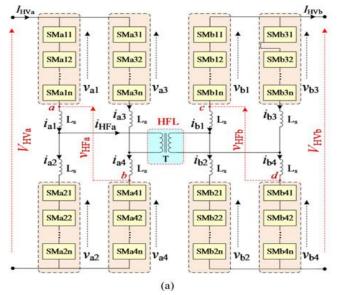

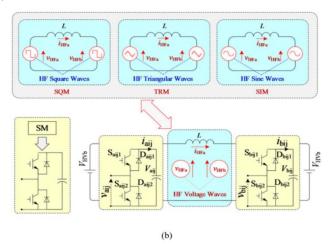

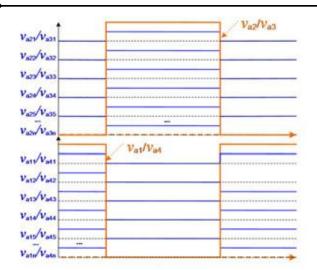

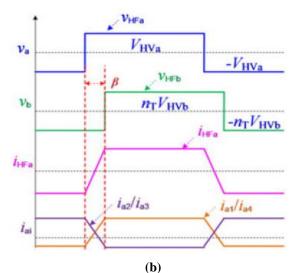

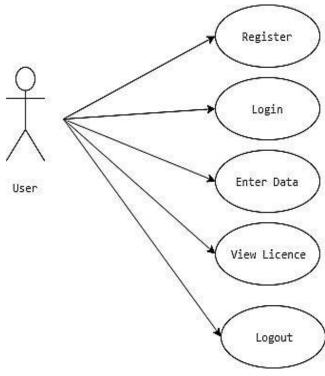

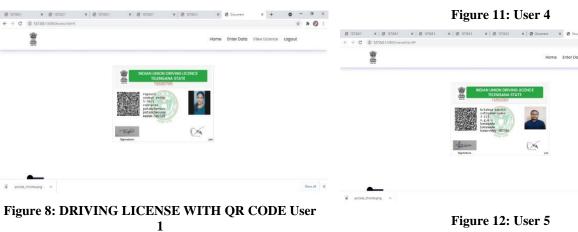

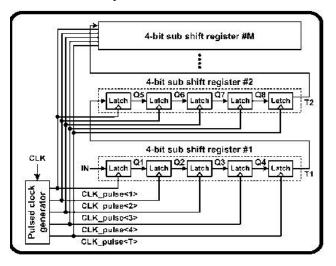

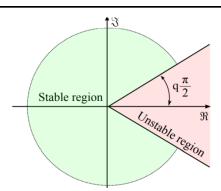

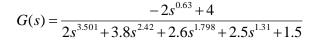

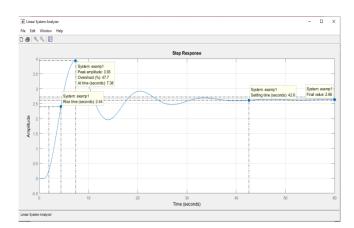

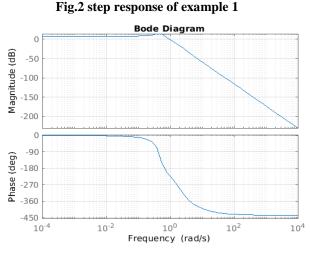

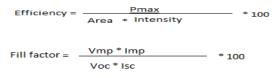

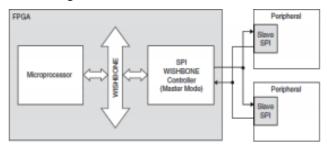

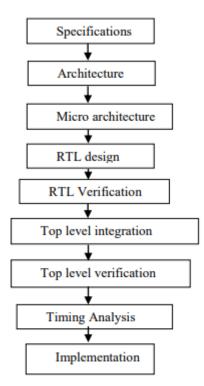

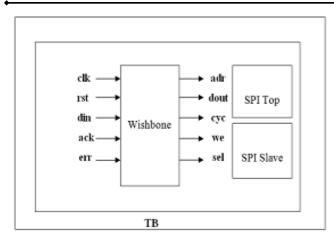

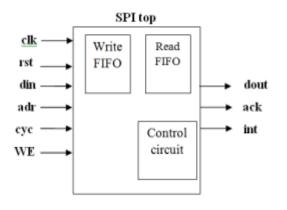

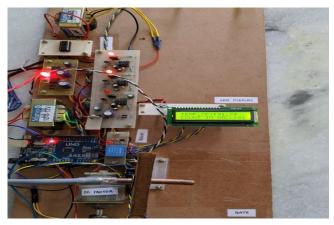

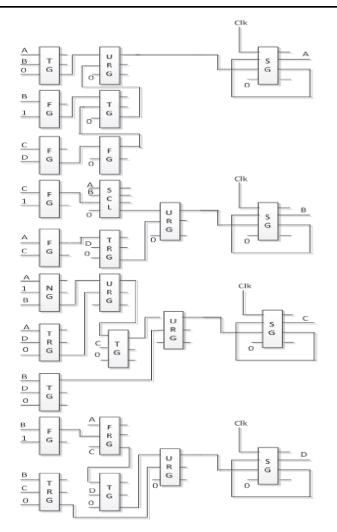

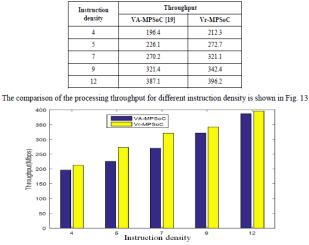

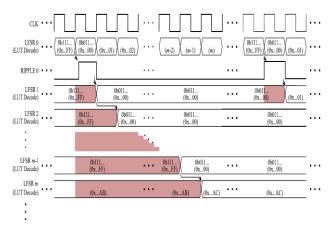

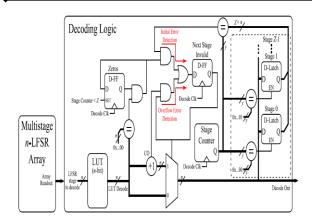

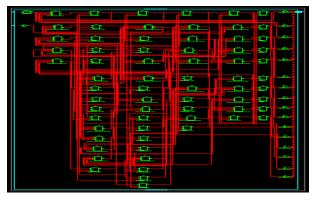

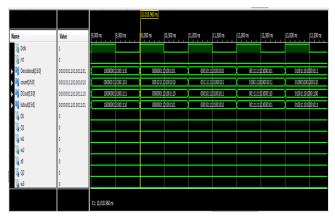

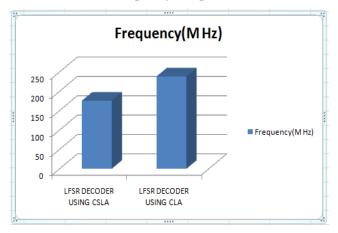

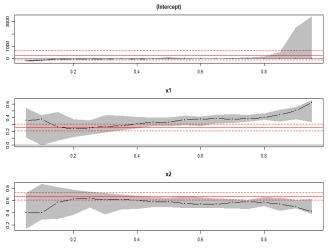

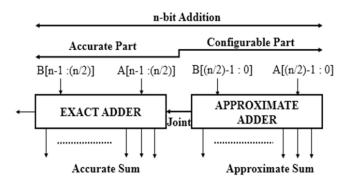

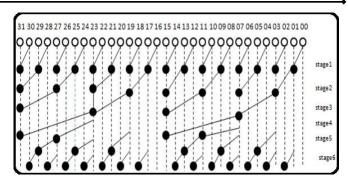

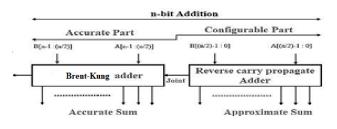

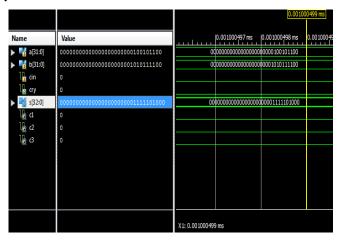

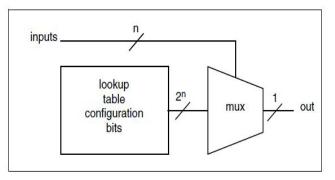

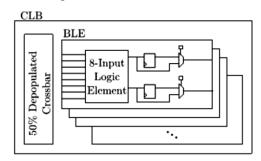

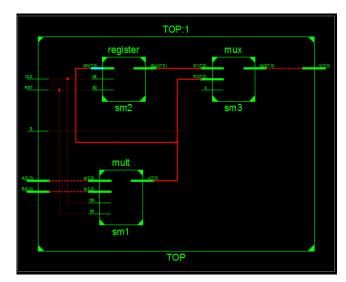

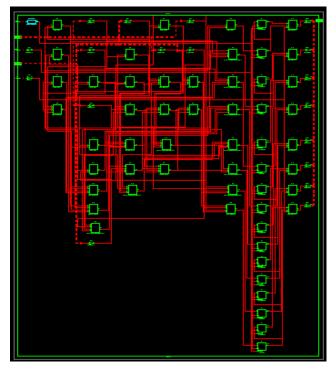

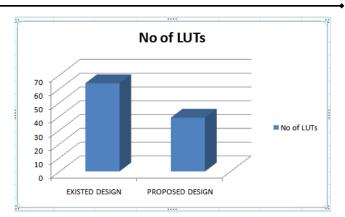

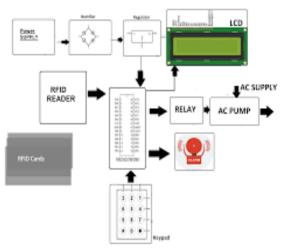

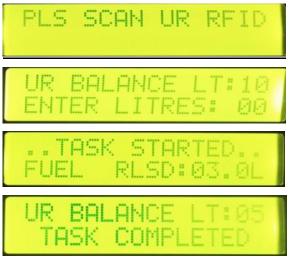

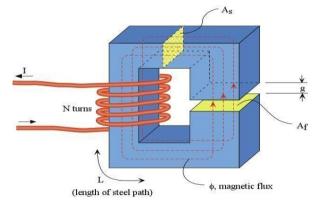

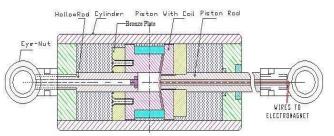

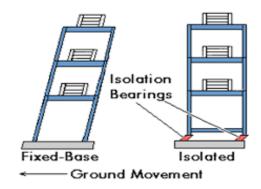

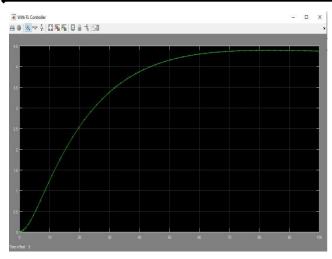

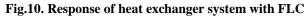

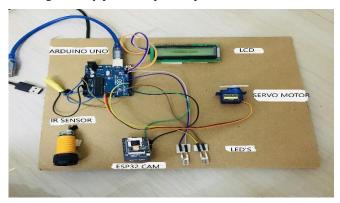

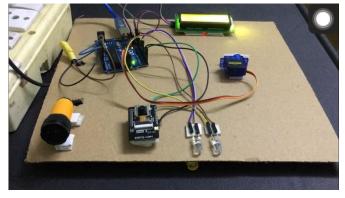

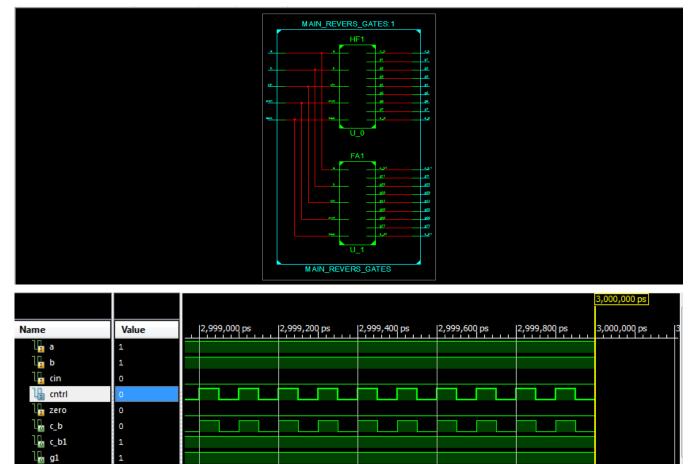

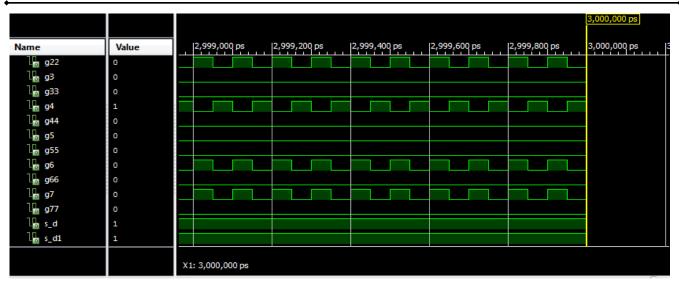

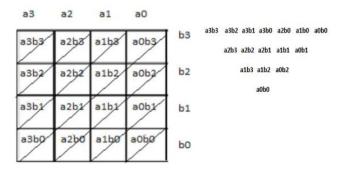

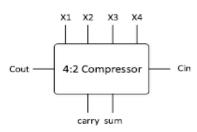

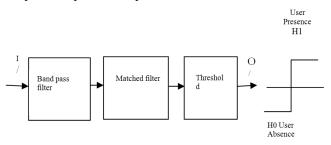

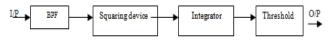

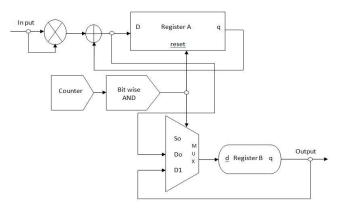

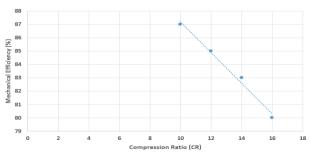

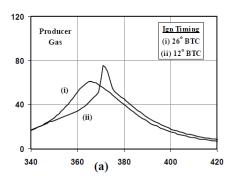

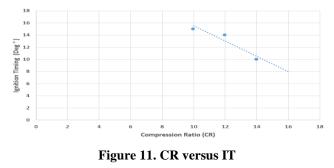

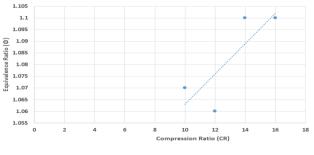

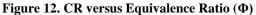

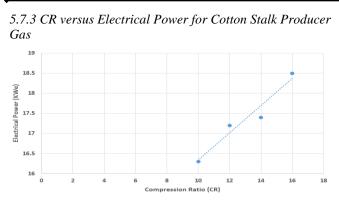

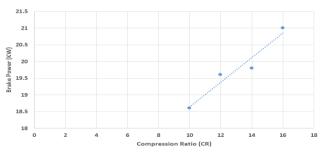

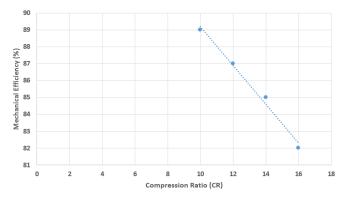

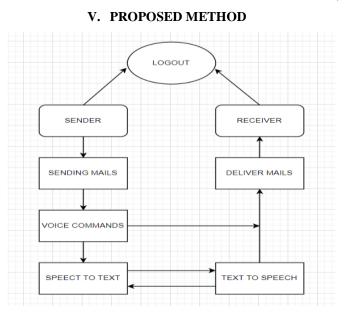

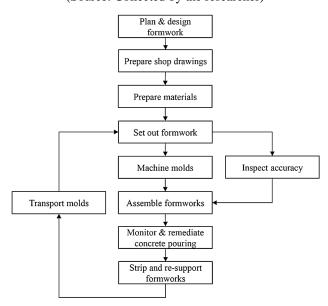

Autophagy degraded lived proteins can also be estimated via non radio active compounds like L-azidohomoalanine (AHA), mode of action includes azide functional group of azidohomoalanine links with the alkyne functional group of dye used in a pulse chase experiment [18]. The fluorescent signal intensity can be determined using techniques like flow cytometry or immuno fluorescent microscopy. This method takes an edge as there is no requirement of handling radioactive materials.